### **Features**

- QTouch® Sensor Channels

- Up to 8 keys

- Integrated Haptic Engine

- Haptic events may be triggered by touch detection or controlled by a host microcontroller over SPI

- Data Acquisition

- QTouchADC key measurement/touch detection method

- Configurable measurement timing and averaging

- Spread spectrum charge transfer

- Raw data from channel measurement can be read over the SPI interface

- GPIO Pins

- 12 dedicated bi-directional GPIO pins, plus up to 4 additional pins (replacing keys)

- Configurable as software PWM Drive, digital inputs or outputs

- Device setup

- Device configuration may be stored in NVRAM

- Operation

- Power-On reset and brown-out detection

- Internal calibrated oscillator

- Key Outline Sizes

- 6 mm x 6 mm or larger (panel thickness dependent); widely different sizes and shapes possible, including solid or ring shapes

- Key Spacing

- 7 mm centre to centre or more (panel thickness dependent)

- Layers required

- One

- Electrode Materials:

- Etched copper, silver, carbon, ITO

- Electrode Substrates:

- PCB materials; polyamide FPCB; PET films, glass

- Panel materials:

- Plastic, glass, composites, painted surfaces (low particle density metallic paints possible)

- Panel Thickness:

- Up to 10 mm glass, 5 mm plastic (electrode size dependent)

- Key Sensitivity:

- Individually configured over SPI interface

- Signal Processing:

- Self-calibration, auto drift compensation, noise filtering

- Patented Adjacent Key Suppression® (AKS®) technology to ensure accurate key detection

- Interface:

- Master/Slave SPI interface, up to 750 kHz

- Object-based communications protocol

- Power:

- 2.0V to 5.5V

- Packages:

- 32-pin 5 x 5 mm MLF RoHS compliant

- 32-pin 7 x 7mm TQFP RoHS compliant

# QTouch 8-key Touch Sensor IC

AT42QT1085

# 1. Pinout and Schematic

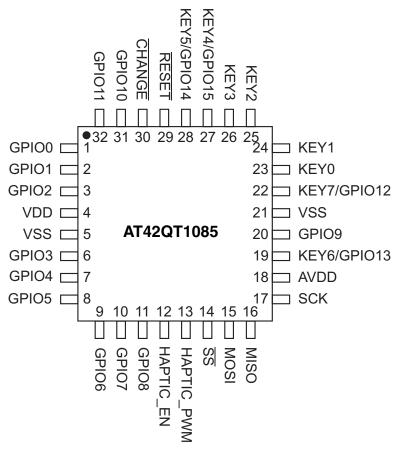

# 1.1 Pinout Configuration

# 1.2 Pinout Descriptions

Table 1-1. Pin Listing

| Pin | Name  | Туре | Comments           | If Unused, Connect To |

|-----|-------|------|--------------------|-----------------------|

| 1   | GPIO0 | I/O  | General Purpose IO | Leave open            |

| 2   | GPIO1 | I/O  | General Purpose IO | Leave open            |

| 3   | GPIO2 | I/O  | General Purpose IO | Leave open            |

| 4   | VDD   | Р    | Power              | -                     |

| 5   | VSS   | Р    | Ground             | -                     |

| 6   | GPIO3 | I/O  | General Purpose IO | Leave open            |

| 7   | GPIO4 | I/O  | General Purpose IO | Leave open            |

| 8   | GPIO5 | I/O  | General Purpose IO | Leave open            |

| 9   | GPIO6 | I/O  | General Purpose IO | Leave open            |

| 10  | GPIO7 | I/O  | General Purpose IO | Leave open            |

| 11  | GPIO8 | I/O  | General Purpose IO | Leave open            |

Table 1-1.

Pin Listing (Continued)

| Pin | Name        | Туре | Comments                        | If Unused, Connect To                |

|-----|-------------|------|---------------------------------|--------------------------------------|

| 12  | HAPTIC_EN   | 0    | Enable pin for haptic amplifier | Leave open                           |

| 13  | HAPTIC_PWM  | 0    | Drive for haptic effects        | Leave open                           |

| 14  | SS          | I    | SPI Enable                      | Pull up to VDD via a 100 kΩ resistor |

| 15  | MOSI        | I    | SPI Data In                     | Leave open                           |

| 16  | MISO        | 0    | SPI Data Out                    | Leave open                           |

| 17  | SCK         | I    | SPI Clock                       | Leave open                           |

| 18  | AVDD        | Р    | Analog Power                    | -                                    |

| 19  | KEY6/GPIO13 | I/O  | Sense pin/General Purpose IO    | Leave open                           |

| 20  | GPIO 9      | I/O  | General purpose IO              | Leave open                           |

| 21  | VSS         | Р    | Ground                          | -                                    |

| 22  | KEY7/GPIO12 | I/O  | Sense pin/General Purpose IO    | Leave open                           |

| 23  | KEY0        | I/O  | Sense pin                       | Leave open                           |

| 24  | KEY1        | I/O  | Sense pin                       | Leave open                           |

| 25  | KEY2        | I/O  | Sense pin                       | Leave open                           |

| 26  | KEY3        | I/O  | Sense pin                       | Leave open                           |

| 27  | KEY4/GPIO15 | I/O  | Sense pin/General Purpose IO    | Leave open                           |

| 28  | KEY5/GPIO14 | I/O  | Sense pin/General Purpose IO    | Leave open                           |

| 29  | RESET       | I    | Reset, internal pull-up         | Leave open                           |

| 30  | CHANGE      | OD   | Status change indicator         | Leave open                           |

| 31  | GPIO10      | I/O  | General Purpose IO              | Leave open                           |

| 32  | GPIO11      | I/O  | General Purpose IO              | Leave open                           |

I Input only O Output only, push-pull I/O Input/output OD Open drain output P Ground or power

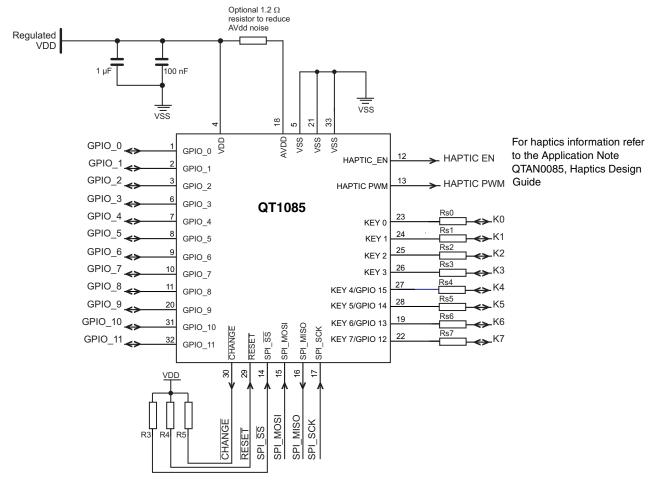

# 1.3 Schematic

Figure 1-1. Typical Circuit

Pin 33, which is the pad on the underside of the device, should be connected to Vss.

Re Figure 1-1 check the following sections for component values:

- Section 3.2 on page 8: Series resistors (Rs0 Rs7)

- Section 3.3 on page 8: Power Supply

# 2. Overview

### 2.1 Introduction

The AT42QT1085 (QT1085) is an easy to use QTouchADC mode sensor IC based on Atmel principles for robust operation and ease of design. It is intended for any touch-key application.

There are four dedicated channels configured as keys (Key 0 – Key 3). Another four channels can be configured as keys or GPIO channels (Key 4 – Key 7 or GPIO 12 – GPIO 15).

There are 12 dedicated GPIO channels (GPIO\_0 – GPIO\_11).

The QT1085 is capable of detecting proximity or touch on the channels configured as keys.

The keys can be constructed in different shapes and sizes. Refer to the *Touch Sensors Design Guide* and Application Note QTAN0079, Buttons, *Sliders and Wheels Sensor Design Guide*, for more information on construction and design methods (both downloadable from the Atmel® website).

Each GPIO channel may be configured as a digital input or output. In output mode, a GPIO pin may be set to output a PWM signal at any of 16 duty cycles (4-bit PWM). The QT1085 allows electrodes to project sense fields through any dielectric such as glass or plastic.

This device has many advanced features which provide for reliable, trouble-free operation over the life of the product. In particular the QT1085 features advanced self-calibration, drift compensation, and fast thermal tracking. The QT1085 can tolerate some fluctuations in the power supply, and in many applications will not require a dedicated voltage regulator.

A full haptics engine is integrated into the device, allowing feedback effects to be triggered on key detection or directly activated by a host microcontroller.

The QT1085 includes all signal processing functions necessary to provide stable sensing under a wide variety of changing conditions. Only a few external parts are required for operation and no external Cs capacitors are required.

The QT1085 modulates its acquisition pulses in a spread-spectrum fashion in order to heavily suppress the effects of external noise, and to suppress RF emissions. This provides greater noise immunity and eliminates the need for external sampling capacitors, allowing touch sensing using a single pin.

# 2.2 Understanding Unfamiliar Concepts

If some of the concepts mentioned in this datasheet are unfamiliar, see the following sections for more information:

• Section 5 "SPI Protocol for Object Protocol Memory Map Access" on page 14.

### 2.3 Resources

The following datasheet provides essential information on configuring the QT1085:

AT42QT1085 Protocol Guide

The following documents may also be useful (available by contacting Atmel's Touch Technology division):

### • Design layout guidelines:

- Application Note: QTAN0079 - Buttons, Sliders and Wheels Sensor Design Guide

### Haptics guidelines:

Application Note: QTAN0085 – Haptics Design Guide

### • Miscellaneous:

- Application Note: QTAN0015 Power Supply Considerations for QT ICs

- Application Note: Atmel AVR3000: QTouch Conducted Immunity

- Design Guide: QTAN0087 Proximity Design Guide

# 2.4 User Interface Layout and Options

### 2.4.1 Keys

There are eight keys available. Each can be individually enabled or disabled by setting a bit in the Key T13 object (one for each key).

### 2.4.2 GPIO Ports

There are 12 dedicated configurable General Purpose Input Output (GPIO) pins. Up to four additional GPIO pins can be achieved by replacing four of the keys. The GPIO pins can be enabled or disabled by setting a bit in the GPIO Configuration T29 object.

### 2.4.3 Guard Channel

A guard channel may be used to prevent accidental touch detection on other keys which share the same Adjacent Key Suppression (AKS) group. The guard channel is made more sensitive than the others in the AKS group through a larger touch electrode area combined with higher gain / lower threshold. The QT1085 remains in Idle mode while a guard channel is in detect, and Touch Automatic Calibration will not occur for a guard key detection.

# 2.5 Proximity Effect

Any channel can function as a proximity sensor, based on hand or body proximity to a product. This is achieved by using a relatively large electrode and tuning the QTouchADC and Threshold configuration options. Refer to QTAN0087, *Proximity Design Guide*, for more information.

### 2.6 SPI Interface

The QT1085 is an SPI slave mode device, utilizing a four-wire full-duplex SPI interface.

There are four standard SPI signals; SS, SCK, MOSI and MISO.

The QT1085 also provides a CHANGE signal to indicate when there is a message waiting to be read. This removes the need for the host to poll the QT1085 continuously.

Communications are performed through Read and Write operations on the Object Protocol memory map.

# 2.7 Operating Modes

Cycle times, Free-run and Sleep modes are controlled by the Power Configuration T7 object settings.

# 2.8 Haptics Engine

The QT1085 can be configured to play a selected haptic effect in response to a touch detection, a state change on a GPIO pin or on demand by the host microcontroller.

A selection of haptic effects is available on the device from the Haptic Event T31 object. The effects include:

Strong Click

Strong Click 60 percent strength

Strong Click 30 percent strength

Sharp Click

Sharp Click 60 percent strength

Sharp Click 30 percent strength

Soft Bump

Soft Bump 60 percent strength

Soft Bump 30 percent strength

**Double Click**

Double Click 60 percent strength

Triple Click

Soft Buzz

Strong Buzz

Effects may be assigned to events, such as a key touch or GPIO state change.

Refer to the *QTAN0085 Haptics Design Guide Application Note* and the *AT42QT1085 Protocol Guide* for more information on this object.

#### 3. Wiring and Parts

#### **Bypass Capacitors** 3.1

One 100 nF bypass capacitor and one 1 µF bypass capacitor must be used on the Vdd digital supply and a 100 nF capacitor on AVDD. The 100 nF capacitors should be mounted close to the device, within 10 mm if possible.

#### 3.2 **Rs Series Resistors**

Series Rs resistors (Rs0 to RS7) are in-line with the electrode connections and are used to limit electrostatic discharge (ESD) currents and to suppress radio frequency interference (RFI). For most applications the Rs resistors will be in the range 4.7 k $\Omega$  to 33 k $\Omega$  each. For maximum noise rejection the value may be up to 100 k $\Omega$ .

Although these resistors may be omitted, the device may become susceptible to external noise or RFI. For details of how to select these resistors refer to Application Note QTAN0002, Secrets of a Successful QTouch™ Design.

#### 3.3 **Power Supply**

See Section 7 on page 19 for the power supply range. If this fluctuates slowly with temperature, the device tracks and compensates for these changes automatically with only minor changes in sensitivity. If the supply voltage drifts or shifts quickly, the drift compensation mechanism will not be able to keep up, causing sensitivity anomalies or false detections. In this situation a dedicated voltage regulator should be included in the circuit.

The QT1085 power supply should be locally regulated using a three-terminal device. If the supply is shared with another electronic system, care should be taken to ensure that the supply is free of digital spikes, sags, and surges, all of which can cause adverse effects.

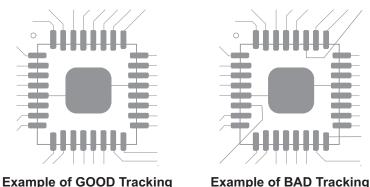

#### 3.4 MLF Package Restrictions

The central pad on the underside of the MLF chip should be connected to ground. Do not run any tracks underneath the body of the chip, only ground. Figure 3-1 on page 8 shows an example of good/bad tracking.

Figure 3-1. Examples of Good and Bad Tracking

8

### 3.5 Oscillator

The device has an internal oscillator. No external oscillator or clock input is required.

# 3.6 PCB Layout and Construction

Refer to Application Note QTAN0079 – *Buttons, Sliders and Wheels Sensor Design Guide* and the *Touch Sensors Design Guide* (both downloadable from the Atmel<sup>®</sup> website), for more information on construction and design methods.

The sensing channels used for the individual keys can be implemented as per the *Touch Sensors Design Guide*.

# 3.7 PCB Cleanliness

Modern no-clean flux is generally compatible with capacitive sensing circuits.

**CAUTION:** If a PCB is reworked in any way, it is almost guaranteed that the behavior of the no-clean flux changes. This can mean that the flux changes from an inert material to one that can absorb moisture and dramatically affect capacitive measurements due to additional leakage currents. If so, the circuit can become erratic and exhibit poor environmental stability.

If a PCB is reworked in any way, clean it thoroughly to remove all traces of the flux residue around the capacitive sensor components. Dry it thoroughly before any further testing is conducted.

# 3.8 Spread-spectrum Circuit

The QT1085 spectrally spreads its frequency of operation to heavily reduce susceptibility to external noise sources and to limit RF emissions.

Bursts operate over a spread of frequencies, so that external fields will have a minimal effect on key operation and emissions are very weak. Spread-spectrum operation works together with the "detect integrator" (DI) mechanism to dramatically reduce the probability of false detection due to noise.

Spread spectrum is hardwired in the chip and is automatically enabled.

# 4. Detailed Operation

### 4.1 Reset

### 4.1.1 Introduction

When starting from power-up or RESET reset there are a few additional factors to be aware of. In most applications the host will not need to take special action.

During a reset all outputs are disabled. To define the levels of  $\overline{CHANGE}$  during reset this pin should pulled up to VDD with a 10 k $\Omega$  to 1M $\Omega$  resistor.

When the initial reset phase ends the CHANGE output is enabled. CHANGE drives low.

A software reset may be requested via the Command Processor T6 object.

### 4.1.2 Delay to SPI Functionality

The QT1085 SPI interface is not operational while the device is being reset. However, SPI is made operational early in the start-up procedure.

After any reset (either via the RESET pin or via power-up), SPI typically becomes operational within 50 ms of RESET going high or power-up. CHANGE is pulled low, and held low until the message server is read by the host micro-controller, to indicate completion of the initialization sequence after power-on or reset.

### 4.1.3 Reset Delay to Touch Detection

After power up or reset, the QT1085 calibrates all electrodes.

During this time, touch detection cannot be reported. Calibration completes after 15 burst cycles, which takes approximately 150 ms, with typical QTouchADC settings.

In total, 200 ms are required from reset or power-up for the device to be fully functional.

### 4.1.4 Mode Setting After Reset

After a reset the device loads configuration settings from nonvolatile memory, either previously stored or default settings.

### 4.2 Calibration

Calibration is the process by which the sensor chip assesses the background capacitance on each channel. Channels are only calibrated on power-up and when:

• The channel is enabled (that is, activated).

OR

- The channel is already enabled and one of the following applies:

- The channel is held in detect for longer than the Touch Automatic Calibration setting (refer to the AT42QT1085 Protocol Guide for more information on TCHAUTOCAL setting in the Touch Configuration T16 object).

**Note:** This does not apply to a guard channel.

- The signal delta on a channel is at least the anti-touch threshold (ATCHCALTHR) in the anti-touch direction (refer to the AT42QT1085 Protocol Guide for more information on the ATCHCALTHR in the PROCG\_TOUCHCONFIG\_T16 object (Touch Configuration T16 object).

- The user issues a recalibrate command.

A status message is generated on the start and completion of a calibration.

Note that the device performs a global calibration; that is, all the channels are calibrated together for power-on or user-requested calibration. Only the individual channel is calibrated for an ATCHCALTHR recalibration.

### 4.3 Communications

### 4.3.1 Introduction

The QT1085 communicates as a slave device over a full-duplex 4-wire (MISO, MOSI, SCK, SS) SPI interface. In addition there is a CHANGE pin which is asserted when a message is waiting to be read:

- Low = Message waiting

- High = No Message waiting

See Section 7.3 on page 19 for details of the SPI Configuration and Timing Parameters.

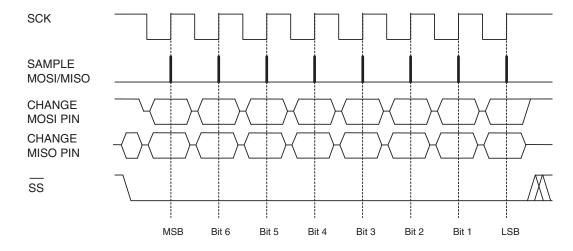

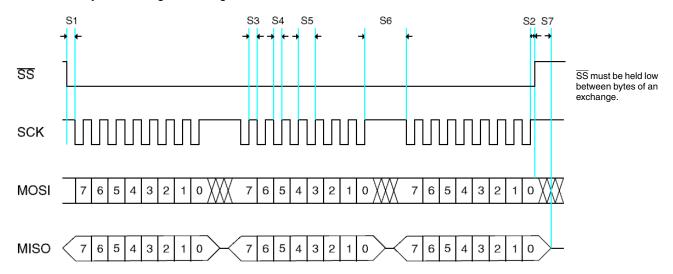

Figure 7-1 and Figure 7-2 on page 20 show the basic timing for SPI operation. The host does the clocking and controls the timing of the transfers from the QT1085.

After the host asserts  $\overline{SS}$  low, it should wait >22 µs in low-power mode before starting SCK; in Free run mode, a delay of 2 µs is sufficient. The QT1085 reads the MOSI pin with each rising edge of SCK, and shifts data out on the MISO pin on falling edges. The host should do the same to ensure proper operation.

SS must be held low for the duration of a communications exchange (a 'Read' or 'Write' operation). To begin a new communications exchange, SS must be pulled high for at least 2 ms after a Read or 10 ms after a Write and then pulled low. SS should be held high when not communicating; if SS is low this is taken as an indication of impending communications.

In this case, extra current is drawn, as the QT1085 does not enter its lowest power Sleep mode.

All timings not mentioned above should be as in Figure 7-2 on page 20.

### 4.3.2 CHANGE Pin

The QT1085 has an open-drain CHANGE pin which notifies the host when a message is waiting to be read.

CHANGE is released after each message has been read through an SPI transfer. If further messages are pending, the QT1085 loads the next one into the Message Handler and then reasserts (pulls low) the CHANGE pin.

### 4.4 Signal Processing

# 4.4.1 Power-up Self-calibration

On power-up, or after reset, all channels are typically calibrated and operational within 200 ms.

#### 4.4.2 **Drift Compensation**

This operates to correct the reference level of each key automatically over time; it suppresses false detections caused by changes in temperature, humidity, dirt and other environmental effects.

The QT1085 drifts as configured in the Touch Configuration T16 object (refer to the AT42QT1085 Protocol Guide for more information).

#### **Detection Integrator Filter** 4.4.3

The device features a touch detection integration mechanism. This acts to confirm a detection in a robust fashion. A counter is incremented each time a touch has exceeded its threshold and has remained above the threshold for the current acquisition. When this counter reaches a preset limit the sensor is finally declared to be touched. If, on any acquisition, the signal is not seen to exceed the threshold level, the counter is cleared and the process has to start from the beginning.

The detection integrator is configured using the touch object Key T13. Refer to the AT42QT1085 Protocol Guide for more information.

#### 4.4.4 Adjacent Key Suppression (AKS) Technology

Adjacent Key Suppression® (AKS®) technology is a patented method used to detect which touch object is touched when objects are located close together. A touch in a group of AKS objects is only indicated on the object with the strongest touch delta. This is assumed to be the intended object. Once an object in an AKS group is in detect, there can be no further detections within that group until the object is released.

AKS is configured using the Key T13 object (refer to the AT42QT1085 Protocol Guide for more information).

Note: If a touch is in detect and then AKS is enabled, that touch will not be forced out of detect. It will not go out of detect until the touch is released. AKS will then operate normally.

#### 4.5 **Operating Modes**

#### 4.5.1 Introduction

The basic operating modes are: Active, Idle and Sleep.

Cycle time for Idle and Active is set by the Power Configuration T7 object, with special cases of 255 for free run and 0 for Sleep.

If a touch is detected, the device switches to free run mode and attempts to perform the detect integrator noise filter (DI) function to completion; if the DI filter fails to confirm a detection the device goes back to Idle mode.

If a key is found to be in detection the part switches to Active mode. If the key is enabled for reporting, a message is generated and CHANGE is asserted (pulled low).

MISO in LP Mode: During the sleep portion of LP mode, MISO floats.

Command During LP Mode: Once set to Sleep (cycle time = 0), the device carries out no acquisitions until the cycle time is changed to >0.

The SS pin must be pulled high in order for the device to enter its lowest power sleep mode. If SS is held low, the device enters a higher power Sleep mode to enable SPI communications.

### 4.5.2 Sleep Mode

Sleep mode offers the lowest possible current drain, in the low microamp region. In this mode no acquisitions are performed.

In Sleep mode Output GPIOs are held in their final state before going to sleep:

- With a 0 percent PWM the GPIO is Off during sleep

- With a 100 percent PWM the GPIO is On during sleep.

If any other PWM is applied then the state is indeterminate (could be On or Off).

If a haptic effect is playing at the time when Sleep mode is entered, the effect is paused and resumed upon exiting Sleep mode if the trigger condition remains true.

### 4.5.3 Supply Sequencing

Vdd and AVdd should be powered by a single supply. Make sure that any lines connected to the device are below or equal to Vdd during power-up. For example, if RESET is supplied from a different power domain to the QT1085's Vdd pin, make sure that it is held low when Vdd is off. If this is not done, the RESET signal could parasitically couple power via the QT1085's RESET pin into the Vdd supply.

# 4.6 Debugging

The QT1085 provides a mechanism for obtaining raw data for development and testing purposes by reading data from the Debug Signals T4 object. Refer to the *AT42QT1085 Protocol Guide* for more information on this object.

# 4.7 Configuring the QT1085

The QT1085 has an object-based protocol that organizes the features of the device into objects that can be controlled individually. This is configured using the Object Protocol common to many of Atmel's touch sensor devices. For more information on the Object Protocol and its implementation on the QT1085, refer to the *AT42QT1085 Protocol Guide*. See also Section 6 on page 17.

# 5. SPI Protocol for Object Protocol Memory Map Access

# 5.1 SPI Signals

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the host and the QT1085. All communication with the device is carried out over the SPI. This is a synchronous serial data link that operates in full-duplex mode. The host communicates with the QT1085 over the SPI using a master-slave relationship, with the QT1085 acting in slave mode.

The SPI uses four logic signals:

- Serial Clock (SCK) output from the host.

- Master Output, Slave Input (MOSI) output from the host, input to the QT1085. Used by the host to send data to the QT1085.

- Master Input, Slave Output (MISO) input to the host, output from the QT1085. Used by the QT1085 to send data to the host.

- Slave Select (SS) active low output from the host.

The SPI signals operate in the following way:

- · SCK Idles high.

- MISO and MOSI are set up on falling edges, read on rising edges.

- SS must be held low throughout the exchange. SS must be pulled high for at least 2 ms after a Read or 10 ms after a Write before another exchange can be initiated.

SCK SAMPLE MOSI/MISO CHANGE MOSI PIN **CHANGE** MISO PIN SS MSB Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 LSB

Figure 5-1. SPI Signals

### 5.2 Communications Protocol

### 5.2.1 MOSI Data

14

A 3 byte command sequence is transmitted by the host on MOSI, setting the memory map address pointer, a Read / Write indication, and the number of bytes which will be read or written.

Read / Write direction is set in Byte 0 Bit 0, where '0' = Write, '1' = Read.

Memory map is addressed in 15 bits, where the lower 7 bits are transmitted at Byte 0 Bits 6 – 1 and the upper 8 bits at Byte 1.

### 5.2.2 MISO Data

Default: 0x55

Returned at each byte on the MISO pin while the 3-byte command sequence is being transmitted on MOSI.

Writing: 0xAA

Returned at each byte on the MISO pin while data is being written by the host on the MOSI pin.

Error: 0xEE

Returned at each byte on the MISO pin in the case where the requested number of bytes has been read or written but an  $\overline{SS}$  high event has not been detected to begin a new exchange. Or, an attempt has been made to Write to a Read-only part of the memory map, in which case the data written for the remainder of the exchange is ignored.

# 5.2.3 Write Operation

Table 5-1. MOSI Data

|          | Bit 7                                     | Bit 6                                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------------------------------------------|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Byte 0   | Memory I                                  | Memory Map Address, Lower 7 Bits (Bits 6 – 0) '0' = W |       |       |       |       |       |       |

| Byte 1   | Memory I                                  | Memory Map Address, Upper 8 Bits (Bits 14 – 7)        |       |       |       |       |       |       |

| Byte 2   | Number o                                  | Number of Data bytes to follow = n                    |       |       |       |       |       |       |

| Byte 3   | Data 0, W                                 | Data 0, Written to Memory Map Address                 |       |       |       |       |       |       |

| Byte 4   | Data 1, Written to Memory Map Address + 1 |                                                       |       |       |       |       |       |       |

|          |                                           |                                                       |       |       |       |       |       |       |

| Byte n+3 | Data n, Written to Memory Map Address + n |                                                       |       |       |       |       |       |       |

Table 5-2. MISO Data

|          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Byte 0   | 0x55  |       |       |       |       |       |       |       |

| Byte 1   | 0x55  |       |       |       |       |       |       |       |

| Byte 2   | 0x55  |       |       |       |       |       |       |       |

| Byte 3   | 0xAA  |       |       |       |       |       |       |       |

| Byte 4   | 0xAA  |       |       |       |       |       |       |       |

|          |       |       |       |       |       |       |       |       |

| Byte n+3 | 0xAA  |       |       |       |       |       |       |       |

# 5.2.4 Read Operation

Table 5-3. MOSI Data

|          | Bit 7    | Bit 6                                          | Bit 5      | Bit 4        | Bit 3       | Bit 2 | Bit 1 | Bit 0   |

|----------|----------|------------------------------------------------|------------|--------------|-------------|-------|-------|---------|

| Byte 0   | Memory N | Map Addres                                     | s, Lower 7 | Bits (Bits 6 | <b>–</b> 0) |       |       | '1' = R |

| Byte 1   | Memory N | Memory Map Address, Upper 8 Bits (Bits 14 – 7) |            |              |             |       |       |         |

| Byte 2   | Number o | Number of Data bytes to follow = n             |            |              |             |       |       |         |

| Byte 3   | N/A      | N/A                                            |            |              |             |       |       |         |

| Byte 4   | N/A      | N/A                                            |            |              |             |       |       |         |

|          |          |                                                |            |              |             |       |       |         |

| Byte n+3 | N/A      | N/A                                            |            |              |             |       |       |         |

Table 5-4. MISO Data

|          | Bit 7                                    | Bit 6                                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|------------------------------------------|------------------------------------------|-------|-------|-------|-------|-------|-------|

| Byte 0   | 0x55                                     |                                          |       |       |       |       |       |       |

| Byte 1   | 0x55                                     | 0x55                                     |       |       |       |       |       |       |

| Byte 2   | 0x55                                     | 0x55                                     |       |       |       |       |       |       |

| Byte 3   | Data 0, R                                | Data 0, Read From Memory Map Address     |       |       |       |       |       |       |

| Byte 4   | Data 1, R                                | Data 1, Read From Memory Map Address + 1 |       |       |       |       |       |       |

|          |                                          |                                          |       |       |       |       |       |       |

| Byte n+3 | Data n, Read From Memory Map Address + n |                                          |       |       |       |       |       |       |

# 6. Getting Started With the QT1085

# 6.1 Communication with the Host

The QT1085 uses an SPI bus to communicate with the host. See Section 5 on page 14 for more information.

# 6.2 Establishing Contact

The host should attempt to read the Information Block information to establish that the device is present and running following power-up or a reset. The host should also check that there are no configuration errors reported.

# 6.3 Using the Object Protocol

The QT1085 has an object-based protocol that is used to communicate with the device. Typical communication includes configuring the device, sending commands to the device, and receiving messages from the device. Refer to the *AT42QT1085 Protocol Guide*.

The host must perform the following initialization so that it can communicate with the QT1085:

- 1. Read the start positions and sizes of all the objects in the QT1085 from the Object Table and build up a list of these addresses.

- 2. Use the Object Table to calculate the report IDs so that messages from the device can be correctly interpreted.

# 6.4 Writing to the Device

See Section 5.2.3 on page 15 for information on the format of the SPI Write operation.

To communicate with the QT1085, write to the appropriate object:

- To send a command to the device, write the appropriate command to the Command Processor T6 object (for example, to send a reset, backup or calibrate command). Refer to the *AT42QT1085 Protocol Guide* for the full list of available commands.

- To configure the device, write to an object. For example, to configure the device's power consumption write to the global Power Configuration T7 object. Some objects are optional and need to be enabled before use.

Refer to the AT42QT1085 Protocol Guide for more information on the objects.

# 6.5 Reading from the Device

See Section 5.2.4 on page 16 for information on the format of the SPI Read operation.

# 6.6 Configuring the Device

The objects are designed such that a default value of zero in their fields is a "safe" value that typically disables functionality. The objects must be configured before use and the settings written to the nonvolatile memory using the Command Processor T6 object. Refer to the *AT42QT1085 Protocol Guide* for more information.

The following objects must be configured before use:

- General Objects

- Power Configuration T7

- QTouchADC Configuration T49

- Touch Objects

- Key T13 (8 instances)

- Signal Processing Objects

- Touch Configuration T16

- Support Objects

- GPIO Configuration T29 (16 instances)

- Haptic Event T31 (8 instances)

Refer to the AT42QT1085 Protocol Guide for information on configuring the objects.

The following objects are also used but require no setting up:

- Debug Objects

- Debug Deltas T2

- Debug References T3

- Debug Signals T4

- General Objects

- Message Processor T5

- Command Processor T6

- Support Objects

- Self Test T25

# 7. Specifications

# 7.1 Absolute Maximum Specifications

| Vdd                                                  | 2V – 5.5V                   |

|------------------------------------------------------|-----------------------------|

| Max continuous pin current, any control or drive pin | 20 mA                       |

| Voltage forced onto any pin                          | -0.5V to (Vdd or AVdd)+0.5V |

| Configuration parameters maximum Writes              | 10,000                      |

**CAUTION:** Stresses beyond those listed under *Absolute Maximum Specifications* may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum specification conditions for extended periods may affect device reliability

# 7.2 Recommended Operating Conditions

| Operating temp                             | -40°C to +85°C  |

|--------------------------------------------|-----------------|

| Storage temp                               | -65°C to +150°C |

| Vdd                                        | 2V – 5.5V       |

| Supply ripple + noise                      | ±20 mV          |

| Cx transverse load capacitance per channel | 1 pF to 30 pF   |

| GPO current                                | <5 mA           |

| Temperature slew rate                      | 10°C per minute |

# 7.3 SPI Bus Specifications

| Parameter                              | Specification                                            |  |  |  |

|----------------------------------------|----------------------------------------------------------|--|--|--|

| Data bits                              | 8 data bits                                              |  |  |  |

| Data transmission                      | Shift out on falling edge<br>Shift in on rising edge     |  |  |  |

| Clock idle                             | High                                                     |  |  |  |

| Maximum clock rate                     | 750 kHz                                                  |  |  |  |

| Minimum time between bytes             | 100 μs                                                   |  |  |  |

| Minimum low clock period               | 666 ns                                                   |  |  |  |

| Minimum high clock period              | 666 ns                                                   |  |  |  |

| Delay between communications exchanges | 2 ms after Read operation<br>10 ms after Write operation |  |  |  |

Figure 7-1. Data Byte Exchange – Signals

Figure 7-2. Data Byte Exchange – Timings

|    | Period                        | Min  | Max | Unit |

|----|-------------------------------|------|-----|------|

| S1 | SS Low to SCK – Free-run mode | 2    | _   | μs   |

| 0. | SS Low to SCK – LP mode       | 22   | _   | μs   |

| S2 | SCK to SS High                | 20   | _   | μs   |

| S3 | SCK Low Pulse                 | 666  | _   | ns   |

| S4 | SCK High Pulse                | 666  | _   | ns   |

| S5 | SCK Period                    | 1332 | _   | ns   |

| S6 | Between Bytes                 | 100  | _   | μs   |

| S7 | SS High to Tristate           | _    | 20  | ns   |

| General        | Min | Max  | Unit |

|----------------|-----|------|------|

| Rise/Fall Time | _   | 1600 | ns   |

| Setup          | 10  | -    | ns   |

| Hold           | 333 | ı    | ns   |

# 7.4 Reset Timings

| Parameter                         | Min | Тур | Max | Units | Notes |

|-----------------------------------|-----|-----|-----|-------|-------|

| Power on to CHANGE line low       |     | 50  |     | ms    |       |

| Hardware reset to CHANGE line low |     | 50  |     | ms    |       |

| Software reset to CHANGE line low |     | 75  |     | ms    |       |

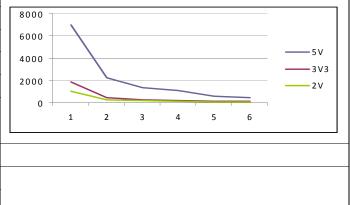

# 7.5 Current Measurements

|           | Keys enabled | DP   | GPIOs 0 to 7   |

|-----------|--------------|------|----------------|

| Config 1: | 8            | 2-1  | Output 60% PWM |

| Config 2: | 8            | 16-8 | Output 60% PWM |

| Config 3: | 8            | 2-1  | Input          |

| Config 4: | 8            | 2-1  | Off            |

| Config | Cycle                      | 5 <b>V</b>              | 3V3  | 2V   |

|--------|----------------------------|-------------------------|------|------|

|        |                            | Current measurements μA |      |      |

| 1a     | Free run (Actual: 9.1ms)   | 5380                    | 1890 | 1025 |

| 1b     | 50 ms                      | 3930                    | 960  | 585  |

| 1c     | 100 ms                     | 3735                    | 840  | 500  |

| 1d     | 150 ms                     | 3660                    | 810  | 473  |

| 1e     | 200 ms                     | 3615                    | 790  | 455  |

| 1f     | 250 ms                     | 3535                    | 778  | 448  |

|        | Cycle                      | 5V                      | 3V3  | 2V   |

| 2a     | Free run (Actual: 20.3 ms) | 5405                    | 1896 | 1050 |

| 2b     | 50 ms                      | 4250                    | 1205 | 730  |

| 2c     | 100 ms                     | 3760                    | 950  | 545  |

| 2d     | 150 ms                     | 3690                    | 890  | 521  |

| 2e     | 200 ms                     | 3710                    | 855  | 486  |

| 2f     | 250 ms                     | 3685                    | 832  | 476  |

|    | Cycle                     | 5V   | 3V3  | 2V   |

|----|---------------------------|------|------|------|

| За | Free run (Actual: 8.6 ms) | 6985 | 1871 | 1014 |

| 3b | 50 ms                     | 2280 | 490  | 326  |

| 3c | 100 ms                    | 1380 | 265  | 188  |

| 3d | 150 ms                    | 995  | 208  | 142  |

| 3e | 200 ms                    | 575  | 150  | 105  |

| 3f | 250 ms                    | 421  | 129  | 84   |

|    | Cycle                     | 5V   | 3V3  | 2V   |

| 4a | Free run (Actual: 7.9 ms) | 6992 | 1881 | 1039 |

| 4b | 50 ms                     | 2240 | 450  | 280  |

| 4c | 100 ms                    | 1360 | 268  | 180  |

| 4d | 150 ms                    | 1060 | 204  | 140  |

| 4e | 200 ms                    | 568  | 126  | 80   |

| 4f | 250 ms                    | 442  | 122  | 78   |

|    | Cycle                     | 5V   | 3V3  | 2V   |

|    | <0>                       | 21   | 18   | 16   |

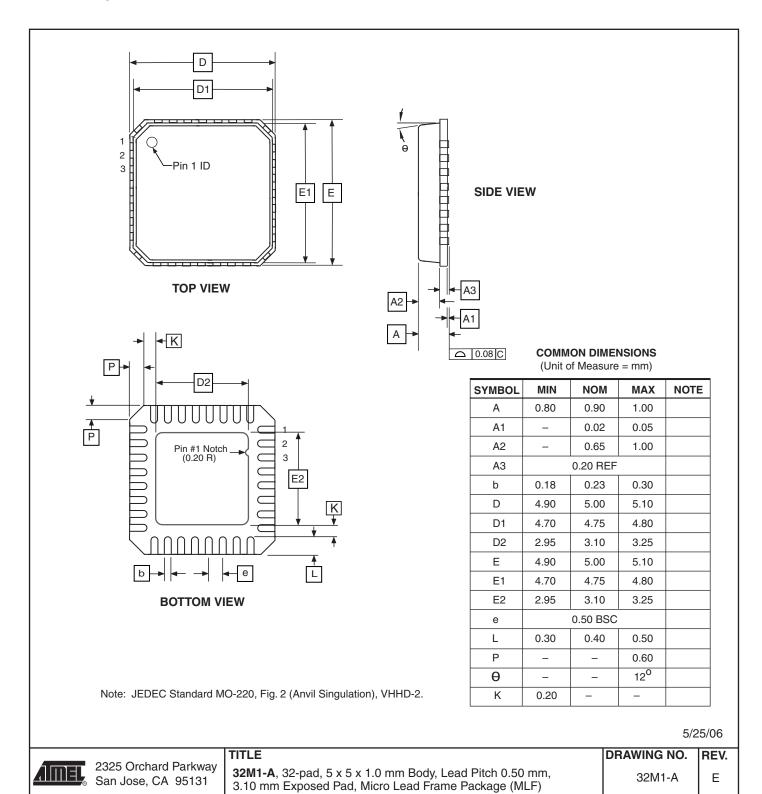

# 7.6 Mechanical Dimensions

### 7.6.1 32-pin 5 x 5 mm MLF

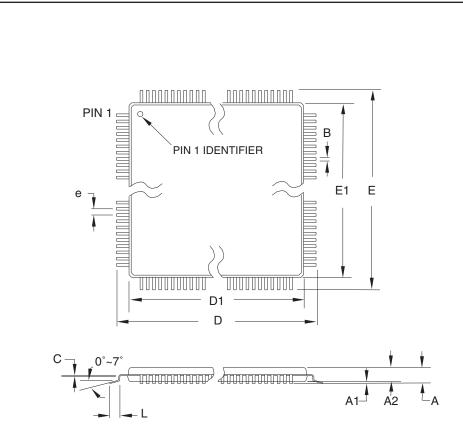

# 7.6.2 32-pin 7 x 7mm TQFP

### **COMMON DIMENSIONS**

(Unit of Measure = mm)

| SYMBOL | MIN  | NOM      | MAX  | NOTE   |

|--------|------|----------|------|--------|

| Α      | _    | _        | 1.20 |        |

| A1     | 0.05 | _        | 0.15 |        |

| A2     | 0.95 | 1.00     | 1.05 |        |

| D      | 8.75 | 9.00     | 9.25 |        |

| D1     | 6.90 | 7.00     | 7.10 | Note 2 |

| E      | 8.75 | 9.00     | 9.25 |        |

| E1     | 6.90 | 7.00     | 7.10 | Note 2 |

| В      | 0.30 | -        | 0.45 |        |

| С      | 0.09 | _        | 0.20 |        |

| L      | 0.45 | _        | 0.75 |        |

| е      |      | 0.80 TYP |      |        |

10/5/2001

Notes:

- 1. This package conforms to JEDEC reference MS-026, Variation ABA.

- 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- 3. Lead coplanarity is 0.10 mm maximum.

| 4 |     |

|---|-----|

| A | MEL |

|   | (9) |

2325 Orchard Parkway San Jose, CA 95131 TITLE

**32A,** 32-lead, 7 x 7 mm Body Size, 1.0 mm Body Thickness, 0.8 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP)

| DRAWING NO. | REV. |

|-------------|------|

| 32A         | В    |

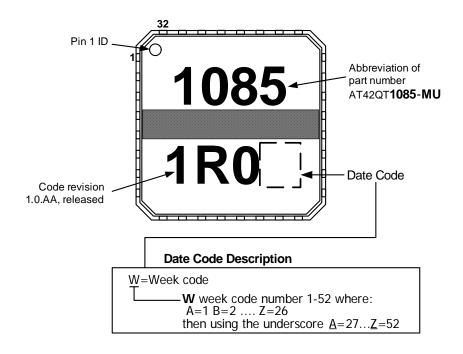

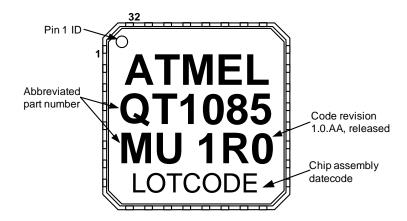

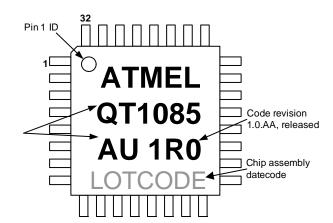

# 7.7 Marking

# 7.7.1 32-pin 5 x 5 mm MLF

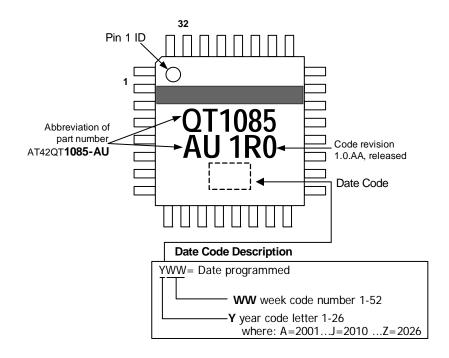

# 7.7.2 32-pin 7 x 7mm TQFP

# 7.8 Part Numbers

| Part Number    | QS Number | Description                                        |

|----------------|-----------|----------------------------------------------------|

| AT42QT1085-MU  | QS588     | 32-pin 5 x 5 mm MLF RoHS compliant                 |

| AT42QT1085-MUR | QS588     | 32-pin 5 x 5 mm MLF RoHS compliant – Tape and reel |

| AT42QT1085-AU  | QS588     | 32-pin 7 x 7mm TQFP RoHS compliant                 |

| AT42QT1085-AUR | QS588     | 32-pin 7 x 7mm TQFP RoHS compliant – Tape and reel |

The part number comprises:

AT = Atmel

42 = Touch Business Unit

QT = Charge-transfer technology

1085= (1) Keys (08) number of channels (5) variant number

AU = TQFP chip

MU = MLF chip

R = Tape and reel

# 7.9 Moisture Sensitivity Level (MSL)

| MSL Rating | Peak Body Temperature | Specifications      |

|------------|-----------------------|---------------------|

| MSL3       | 260°C                 | IPC/JEDEC J-STD-020 |

# **Associated Documents**

- QTAN0079 Buttons, Sliders and Wheels Touch Sensors Design Guide

- QTAN0087 Proximity Design Guide

- Atmel AVR3000: QTouch Conducted Immunity Application Note

# **Revision History**

| Revision Number             | History                                                        |

|-----------------------------|----------------------------------------------------------------|

| Revision AX – May 2011      | Initial release for firmware version 0.4                       |

| Revision BX – August 2011   | Firmware version 0.5 Amendments and clarifications to text.    |

| Revision CX – December 2011 | Firmware version 1.0.AA Amendments and clarifications to text. |

**Notes**

### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600

### International

Atmel Asia

Unit 01-05 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong Kowloon HONG KONG

Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

**Touch Technology Division**

1560 Parkway Solent Business Park Whiteley Fareham Hampshire PO15 7AG UNITED KINGDOM Tel: (+44) 844 894 1920 Fax: (+44) 1489 557 066 Atmel Munich GmbH

Business Campus Parkring 4 D- 85748 Garching b. MUNICH

Tel: (+49) 89-31970-111 Fax: (+49) 89-3194621 Atmel Japan

16F Shin-Osaki Kangyo Building 1-6-4 Osaki

Shinagawa-ku, Tokyo 141-0032

JAPAN

Tel: (+81) (3) 6417-0300 Fax: (+81) (3) 6417-0370

### **Product Contact**

Web Site www.atmel.com Technical Support touch@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2010 – 2011 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, QTouch<sup>®</sup> and others are registered trademarks, QT<sup>™</sup> and others are trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be registered trademarks or trademarks of others.